Research Article | Volume 10, Issue 3 | Pages 572-578 | e-ISSN: 2347-470X

## Digital Hysteresis Control Algorithm for Switched Inductor Quasi Z-Source Inverter with Constant Switching Frequency

#### V. Malathi<sup>1</sup>, Dr. S. Sentamil Selvan<sup>2</sup> and Dr. S. Meikandasivam<sup>3</sup>

<sup>1</sup>Research Scholar, Department of EEE, Sri Chandrasekharendra Saraswathi Viswa Mahavidyalaya, Kanchipuram, India, vmalathi@kanchiuniv.ac.in.

<sup>2</sup>Associate Professor, Department of EEE, Sri Chandrasekharendra Saraswathi Viswa Mahavidyalaya, Kanchipuram, India, sentamilselvan.s@kanchiuniv.ac.in.

<sup>3</sup>Associate Professor, School of Electrical Engineering, VIT University, Vellore, India, meikandasivam.s@vit.ac.in.

\*Correspondence: V. Malathi; Email: vmalathi@kanchiuniv.ac.in.

ABSTRACT- In this paper, a digital hysteresis current limit controller is developed for Switched Inductor Quasi Z-Source Inverter (SLQZSI). Traditional methods like hysteresis current fixed limit and adjustable hysteresis current limit techniques changes the hysteresis bandwidth in accordance to modulating frequency and gradient of reference current. The operating shifting frequency of typical approaches oscillates and crosses the intended steady shifting frequency under noise. It leads to undesirable heavy interference between the phases and more power loss. In the planned digital hysteresis current limit technique, the hysteresis current limit is calculated by resolving the optimization problem. In the proposed approach the operating shifting frequency is kept same or inferior to the intended steady shifting frequency even under noise. Hence the planned digital hysteresis current limit algorithm maintains the output current steady and power loss is minimized which is not promised by the conservative techniques. To compare different control strategies in terms of nature of operating switching frequency and harmonic performance simulations are built on the MATLAB/SIMULINK.

**Keywords:** Digital Control, Hysteresis Control, Optimization problem, SLQZSI, Switching frequency, Total Harmonic Distortion.

crossref

CROSSREF.ORG

#### ARTICLE INFORMATION

**Author(s)**: V. Malathi, Dr. S. Sentamil Selvan and Dr. S. Meikandasivam

Received: 23/06/2022; Accepted: 15/08/2022; Published: 07/09/2022;

e-ISSN: 2347-470X; Paper Id: IJEER220632; Citation: 10.37391/IJEER.100327

Webpage-link:

https://ijeer.for exjournal.co. in/archive/volume-10/ijeer-100327.html

**Publisher's Note:** FOREX Publication stays neutral with regard to Jurisdictional claims in Published maps and institutional affiliations.

#### 1. INTRODUCTION

Website: www.ijeer.forexjournal.co.in

Now a days in most applications such as enabling wider propagation of non-conventional energy production, [1,2] the recognition of new grid ideas with elevated effectiveness [3,4], inverters and their controllers have been receiving increased attention. There are three major classes of current control techniques, for instance sinusoidal triangle Pulse Width Modulation (PWM), predictive dead beat, hysteresis current control are developed over last few decades. The asynchronous sinusoidal delta PWM procedure needs a Proportional Integrator (PI) regulator to vary the current mismatch and often causes inevitable delay. The deadbeat predictive control procedure is extremely reliant on the precision of the predictive model, but is very convoluted to execute on the contrary, Hysteresis current control is easier to apply and has rapid vibrant response. This technique does not involve any particulars regarding the system speed and accuracy, hence strength of the procedure is enhanced. Therefore, this hysteresis

current control procedure meets applications in a wide range of switching inverters.

### 2. LITERATURE REVIEW

In Hysteresis current control approach, the switching pulse is obtained by analyzing the real current and reference current, hence current mistake lies inside the acceptance current limit. In symphonic hysteresis current controllers [5,6], the hysteresis current limit is preset to a definite rate. This creates the shifting frequency to fluctuate with the purpose of include the current wave inside the limit. In adaptive hysteresis current control approach the current limit is managed adaptively in every shifting modulation cycle.

In digital hysteresis current control, a suitably high sampling frequency is required to operate the inverter switches with exact shifting time. The ripple current is contrary comparative to production inductance and directly comparative to diversity among the DC and output voltages. So ripple current shifts fastly during every switching modulation. In the sampling time, the hysteresis current limit is not realized awaiting the appearance of subsequent data sample. A small sampling rate leads to a significant overrun of the hysteresis limit ripple current [8,9].

The elevated switching rate has numerous advantages such as lesser ripple current and quicker transient response, for example, if a motor is hastened starting idle to rated speed, and in order to have small current alteration the inverter switches [10,11] are made to operate at their highest possible switching

Research Article | Volume 10, Issue 3 | Pages 572-578 | e-ISSN: 2347-470X

components and are enforced to transform its on – off states at a frequency outside its border. Because of presence of noise, short circuit problem may arise and leading to damage of shifting devices. Hence utmost care should be taken to control properly the hysteresis current band, making the frequency of the switching mechanisms not to go beyond their peak achievable switching frequency [12,13].

The typical approach uses the estimated voltage on the moment while the switches begin a current modulation cycle. Especially with the noise, the traditional approach [14,15] is not guaranteed to go beyond the highest switching frequency limit. The study of all literature review does not reveal the digital hysteresis control limit technique for SLQZSI using optimization resolution. The present work illustrates a novel digital hysteresis current control approach which considers the feedback data from the proceeding modulation cycle in to account. This technique keeps the switching frequency stable and constantly under the peak possible switching frequency even noise is present.

In this research work, *Section 3* deals with classical hysteresis current fixed limit control approach, *Section 4* presents Typical Adjustable Hysteresis Current Control Technique, *Section 5* introduces Digital Hysteresis Current Control Technique, *Section 6* shows the simulation results and *Section 7* summarizes conclusions.

## 3. CLASSICAL HYSTERESIS STABLE LIMIT CURRENT CONTROL TECHNIQUE

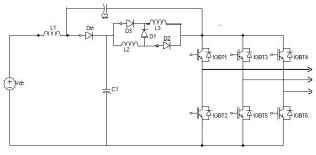

Consider the switching devices  $S_1$  and  $S_2$  in one leg phase of SLQZS inverter circuit. As seen in Figure 1, the output is connected to the Induction Motor ac voltage  $V_m$ . The DC voltage is supplied by a DC source has the value of  $V_{dc}$ . The switching devices  $S_1$  and  $S_2$  controls inverter output current  $i_L$  to track the given reference current  $i_{ref}$  current ripple filter removes the ripple content of output current  $i_L$  and output current  $i_0$  enters into motor without a ripple component. In Table 1, Inputs and Outputs of inverter are shown along with the state of the switches.

Figure 1: SL-QZSI Topology

Table 1: Switching States and their respective outputs

Website: www.ijeer.forexjournal.co.in

| manic 1. Switching States and then respective outputs |       |       |           |       |  |  |

|-------------------------------------------------------|-------|-------|-----------|-------|--|--|

| Half Period                                           | $S_1$ | $S_2$ | $V_{dc}$  | $i_L$ |  |  |

| Positive                                              | ON    | OFF   | $V_{dc}$  | Rise  |  |  |

| Negative                                              | OFF   | ON    | $-V_{dc}$ | Fall  |  |  |

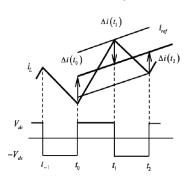

The Tolerance current limit is set to a definite assessment  $\Delta i_b$ . No shifting occurs, if the output current  $i_L$  is among the higher and lesser boundary. The current begins to diminish when the switch  $S_1$  is twisted off after that switch  $S_2$  is twisted on, if the estimated output current passes over the upper limit of hysteresis band  $(\Delta i_{ref} + \Delta i_b)$ . The  $S_1$  is turned ON, the switch  $S_2$  is twisted OFF and current begins to rising if the calculated output current moves below the lesser boundary of hysteresis limit  $(\Delta i_{ref} - \Delta i_b)$  as shown in *figure 2*.

Figure 2: Stable band hysteresis current control

The hysteresis current limit is inversely proportional to shifting frequency and directly proportional to current ripple. As a result, increasing the hysteresis current limit value increases the current ripple, whereas decreasing the hysteresis current limit value increases the switching loss. In analogue regulators, the current swell is forever maintained inside the hysteresis group. Here digital controllers, the current limit must be selected to meet the criteria.

$$\Delta i_b > \max\left(\frac{di_{ref}}{dt}\right) \frac{1}{f_{sp}}$$

[1]

Where  $f_{sp}$  is the sampling frequency. The highest shifting frequency  $f_{sw\_max}$  must be lesser compared to the partially the sampling frequency.

$$f_{sw\_max} \le \frac{1}{2} f_{sp} \tag{2}$$

Stable limit hysteresis current Controller is very simple to implement, fast and stable response and is independent to changes in parameters of the load and power supply. The maximum peak current ripple is organized by any means the points on primary frequency signal by varying the switching frequency.

## 4. TYPICAL ADJUSTABLE HYSTERESIS CURRENT CONTROL TECHNIQUE

Symphonic hysteresis current technique introduces an undesirable heavy interference between phases in three-phase systems. So as to get better, an adjustable hysteresis current organized approach is implemented. In every switching modulation cycle, the current limit is not fixed but is controlled adaptively. Current limit is controlled based on the calculated output voltage values and the targeted switching constant frequency.

The current error  $\Delta i(t)$  at time 't' is given by the expression

$$\Delta i(t) = i_L(t) - i_{ref}(t)$$

[3]

Research Article | Volume 10, Issue 3 | Pages 572-578 | e-ISSN: 2347-470X

Where  $i_L(t)$  and  $i_{ref}(t)$  are the inverter output and reference current at time instant't'.

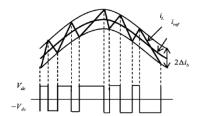

The current error at time instant  $t_0$  is  $\Delta i(t_0)$  as shown in Figure 3. Let at ' $t_0$ ' the output current  $i_L$  tends to pass over the lower hysteresis band, Switch  $S_1$  is closed during  $[t_0, t_1)$ intervals and open during  $[t_1, t_2]$  intervals. Positive turn on and negative turn off durations are the terms for these intervals.

Figure 3: Typical adjustable hysteresis current control

The dynamic formula for output current can be expressed as:

$$\frac{di_L(t)}{dt} = \frac{v_{dc}(t) - v_m(t)}{L}$$

[4]

$$\frac{di_L(t)}{dt} = \frac{v_{dc}(t) - v_m(t)}{L}$$

[4]

$$v_{dc}(t) = \begin{cases} v_{dc} & \text{if } S_1 \text{is } ON \\ -v_{dc} & \text{if } S_1 \text{ is } OFF \end{cases}$$

The output current gradients in the ON and OFF phases are defined as  $I_{ON}$  and  $I_{OFF}$  respectively.

Now during the switching modulation period  $[t_0, t_2]$ , output voltage is slowly varying. Hence the output current gradients (4) be able to be stated like

$$\dot{I}_{ON} = \frac{di_L(t)}{dt} = \frac{v_{dc} - v_m(t_0)}{L} \quad \text{for } t \in [t_0, t_1)$$

$$\dot{I}_{OFF} \triangleq \frac{di_L(t)}{dt} = \frac{-v_{dc} - v_m(t_0)}{L} \quad \text{for } t \in [t_1, t_2)$$

[7]

$$\dot{I}_{OFF} \triangleq \frac{di_L(t)}{dt} = \frac{-v_{dc} - v_m(t_0)}{L} \quad \text{for } t \in [t_1, t_2)$$

[7]

During the positive turn on and negative turn off cycles, the current mistakes are given by

$$\Delta i(t_1) = i_L(t_1) - i_{ref}(t_1)$$

[8]

$$= i_{ref}(t_0) + \Delta i(t_0) + \dot{I}_{ON} T_{ON} - i_{ref}(t_1)$$

[9]

$$\Delta i(t_2) = i_L(t_2) - i_{ref}(t_2)$$

[10]

$$= i_{ref}(t_0) + \Delta i(t_0) + (\dot{l}_{ON}T_{ON} + \dot{l}_{OFF}T_{OFF}) - i_{ref}(t_2)$$

[11]

For the switch  $S_1$ ,  $T_{ON}$  and  $T_{OFF}$  are the on and off periods and they are expressed as

$$T_{ON} = t_1 - t_0 ag{12}$$

$$T_{ON} = t_1 - t_0$$

[12]

$T_{OFF} = t_2 - t_1$  [13]

During the modulation period the reference current slowly varies and it can be approximated as

$$i_{ref}(t_1) = i_{ref}(t_0) + \dot{I}_{ref}(t_0)T_{ON}$$

[14]

$$i_{ref}(t_2) = i_{ref}(t_0) + \dot{I}_{ref}(t_0)(T_{ON} + T_{OFF})$$

[15]

$$i_{ref}(t_2) = i_{ref}(t_0) + \dot{I}_{ref}(t_0)(T_{ON} + T_{OFF})$$

$$\dot{I}_{ref}(t_0) = \frac{di_{ref}(t)}{dt} \Big|_{t=t_0}$$

[15]

The current errors can be determined by substituting equations [14] and [15] in [9] and [11]

$$\Delta i(t_1) = \Delta i(t_0) - \dot{\bar{I}}_{ON} T_{ON}$$

[17]

$$\Delta i(t_2) == \Delta i(t_0) + \dot{I}_{ON} T_{ON} + \dot{I}_{OFF} T_{OFF}$$

[18]

Where  $\dot{I}_{ON}$  and  $\dot{I}_{OFF}$  are the current mistake gradient in positive turn on and negative turn off cycles and are represented as

$$\dot{I}_{ON} = \dot{I}_{ON} - \dot{I}_{ref}(t_0) = \frac{v_{dc} - v_m(t_0)}{L} - \dot{I}_{ref}(t_0)$$

$$\dot{I}_{OFF} = \dot{I}_{OFF} - \dot{I}_{ref}(t_0) = \frac{-v_{dc} - v_m(t_0)}{L} - \dot{I}_{ref}(t_0)$$

[20]

$$\dot{I}_{OFF} = \dot{I}_{OFF} - \dot{I}_{ref}(t_0) = \frac{-v_{dc} - v_m(t_0)}{L} - \dot{I}_{ref}(t_0)$$

[20]

The targeted constant switching frequency is denoted as  $f_{sw}$ . In the typical adjustable hysteresis current control approach, the hysteresis current limit  $\Delta i_h(t_0)$  is deduced by using the following conditions:

$$\Delta i(t_1) - \Delta i(t_0) = 2\Delta i_b(t_0)$$

[21]

$$\Delta i(t_1) - \Delta i(t_0) = 2\Delta i_b(t_0)$$

[21]

$\Delta i(t_2) - \Delta i(t_1) = -2\Delta i_b(t_0)$  [22]

$$T_{ON} + T_{OFF} = T_{sw} ag{23}$$

where  $T_{SW} = \frac{1}{f_{SW}}$  is the targeted constant switching time. Inserting equations [21]–[23] into

Equations [17] and [18], the hysteresis current band is deduced

$$\Delta i_b(t_0) = \frac{1}{2} \frac{i_{ON} i_{OFF}}{i_{OFF} - i_{ON}} T_{SW}$$

[24]

By inserting equations [19] and [20] into Equation [24], the hysteresis limit in Equation [24] also be drafted as:

$$\Delta i_b(t_0) = \frac{V_{dc} T_{sw}}{4L} \left( 1 - m^2(t_0) \right)$$

$$m(t_0) = \frac{1}{V_{dc}} \left( v_m(t) + L \dot{I}_{ref}(t) \right)$$

[25]

$$m(t_0) = \frac{1}{V_{dc}} \left( v_m(t) + L\dot{l}_{ref}(t) \right)$$

[26]

while the inverter is working in the presence of noise, the negative half switching time  $T_{OFF}$  pre in the earlier modulation shorter than the designed parameter, then working shifting frequency exceeds the highest possible shifting frequency.

### **5. DIGITAL HYSTERESIS CURRENT** CONTROL TECHNIQUE

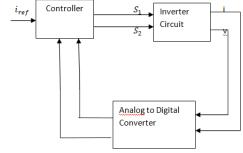

Figure 4 shows the arrangement of digital control technique. ADC measures and samples output voltage and current. These samples are applied for figuring ON/OFF pulses of switches  $S_1$ and  $S_2$ .

Figure 4: Arrangement of Digital Hysteresis Current Control Technique

Research Article | Volume 10, Issue 3 | Pages 572-578 | e-ISSN: 2347-470X

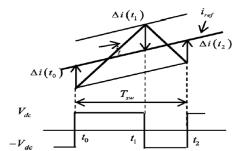

At instant to if the output current crosses the lower band  $(\Delta i_{ref} + \Delta i_h)$  and the switch S<sub>1</sub> is about to switch ON as depicted in *figure 5*. The negative turn off cycle of switch  $S_1$  in the previous modulation time  $T_{OFF\ pre}$

Figure 5: Digital hysteresis current control

This method provides an optimization problem fo computing hysteresis band as

$$T_{OFF}_{pre} = t_0 - t_{-1} [27]$$

$$(i)T_{OFF}_{nre} + T_{ON} \ge T_{sw}$$

[28]

$$(ii)T_{ON} + T_{OFF} = T_{sw} ag{29}$$

$$(iii)\Delta i_b = \Delta i(t_1) = -\Delta i(t_2)$$

[30]

$$(iv)\Delta i_b \ge \Delta i_{conv}$$

[31]

Minimise

$$J = (\Delta i(t_1))^2 + (\Delta i(t_2))^2$$

[32]

where  $\Delta i_{conv}$  is the hysteresis current limit estimated with the typical approach while in equation [24], and objective function is denoted as J.

Limitation constraints (i) and (ii) justify the working shifting frequency to exist identical otherwise lesser than targeted moment shifting frequency. Condition (iii) sets the mean magnitude of output current similar to the mention current through the shifting modulation cycle. Constraint (iv) prevents the amount produced current as of diverging as of the reference current. In every shifting modulation cycle, the power loss from the inverter is represented by the objective function J. The hysteresis limit is estimated to minimize energy loss J.

Equations [17] and [18] may be drafted like

$$T_{ON} = \frac{1}{\hat{t}_{ON}} \left( \Delta i(t_1) - \Delta i(t_0) \right)$$

$$T_{OFF} = \frac{1}{\hat{t}_{OFF}} \left( \Delta i(t_2) - \Delta i(t_1) \right)$$

[33]

$$T_{OFF} = \frac{1}{\tilde{I}_{OFF}} \left( \Delta i(t_2) - \Delta i(t_1) \right)$$

[34]

Inserting equations [33] and [34] into equation [27]-[32], the optimization problem can be drafted as:

$$(i) \Delta i(t_1) \ge \dot{I}_{ON} \left( T_{sw} - T_{OFF\_pre} \right) + \Delta i(t_0)$$

[35]

$$(ii)\left(1 - \frac{i_{ON}}{i_{OFF}}\right)\Delta i(t_1) + \frac{i_{ON}}{i_{OFF}}\Delta i(t_2) \ge i_{ON}T_{sw} + \Delta i(t_0) [36]$$

$$(iii) \Delta i(t_1) = -\Delta i(t_2) = \Delta i$$

$$[37]$$

$$(iii) \Delta i(t_1) = -\Delta i(t_2) = \Delta i$$

[37]

$$(iv) \, \Delta i_b \ge \Delta i_{conv} \tag{38}$$

Minimise

$$J = (\Delta i(t_1))^2 + (\Delta i(t_2))^2$$

[39]

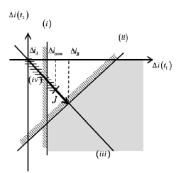

Figure 6: Hysteresis current band domain and optimal solution

The constraints make the optimization problem linear. Using Graphical method, the constraints are solved. The restriction conditions (i)-(iv) are depicted in figure 6 as a black patch in the phase plane  $(\Delta i(t_1), \Delta i(t_2))$  indicating the viable region. The separation from the initial stage -plane to point  $(\Delta i(t_1), \Delta i(t_2))$  gives the objective function J. Hence from the graph the optimal solution is the point  $(\Delta i(t_1)s, \Delta i(t_2)s)$  on the viable region, close near the initial value. The optimal result be able to determine like

$$\Delta i_{opt} = max(\Delta i_{conv}, \Delta i_{A}, \Delta i_{B})$$

[40]

Where  $\Delta i_{conv}$ ,  $\Delta i_A$   $\Delta i_B$  be the points which fulfill combine limitation constraints (i, iii), (ii, iii), (iv, iii), correspondingly, and are known as

$$\Delta i_A = \dot{I}_{ON} \left( T_{SW} - T_{OFF} |_{nre} \right) + \Delta i(t_0)$$

[41]

$$\Delta i_{A} = \dot{I}_{ON} \left( T_{SW} - T_{OFF\_pre} \right) + \Delta i(t_{0})$$

$$\Delta i_{B} = \frac{i_{ON} T_{SW} + \Delta i(t_{0})}{1 - 2\frac{\dot{I}_{ON}}{I_{OFF}}}$$

$$\Delta i_{conv} = \frac{1}{2} \frac{\dot{I}_{ON} \dot{I}_{OFF}}{I_{OFF} - I_{ON}} T_{SW}$$

$$[43]$$

$$\Delta i_{conv} = \frac{1}{2} \frac{i_{ON} i_{OFF}}{I_{OFF} - I_{ON}} T_{sw}$$

[43]

When the optimal solution is at  $\Delta i_A$ , negative turn off cycle  $T_{OFF}$  pre is the previous switching modulation was lesser than normal value. To satisfy the condition (i), hysteresis current band is to be broadened. When the optimal solution is at  $\Delta i_R$ , average output current deviated from reference current. To satisfy the condition (ii), hysteresis current band is to be broadened. Whenever the most favourable resolution is at  $\Delta i_{conv}$  it signifies to *condition* (i) along with (ii) have been met, and the hysteresis current limit ought to be elicited to relentless position as in typical approach.

### **886. RESULTS AND DISCUSSION**

To judge the performance of planned approach and to compare with the typical approach, simulations have been carried out using MATLAB. The transistors available in inverter circuit were represented by IGBT. The output inductance L=1mH and filter capacitor of C= $10\mu F$ . The inverter was powered by dc  $v_{dc}$  =100V and an ac voltage of  $V_m$ voltage of =15  $\sqrt{2} \sin(100\pi t)$  .  $i_{ref}$  =10  $\sin(100\pi t)$  were used as reference current,  $f_{sp}$  =2MHz was the sampling frequency of analog to digital converter.

Research Article | Volume 10, Issue 3 | Pages 572-578 | e-ISSN: 2347-470X

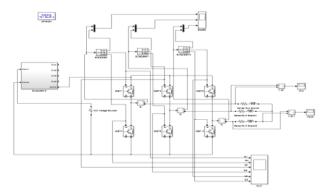

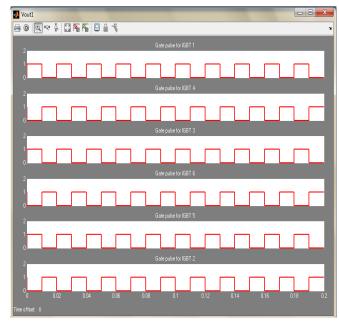

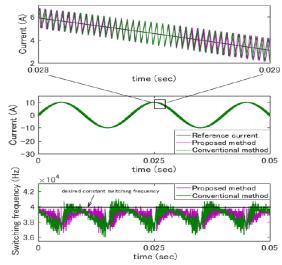

Noise is assumed as White noise with Variance of 0.01A. This can arise from a current sensor or an analog to digital Converter. *Figure* 7 displays simulation diagram of SLQZSI with digital Hysteresis control. *Figure* 8 displays gate pulses for IGBT switches generated by planned technique. In *Figure* 9 Current Vs time curve shows the hysteresis current limit response for intended shifting frequency at 40KHZ. The switching frequency Vs time curve displays the nature of operating shifting frequency among planned and traditional approach. It is noticed that the response of operating frequency crosses the intended steady switching frequency of 40 kHz for typical method and it lies below the intended steady switching frequency for planned method.

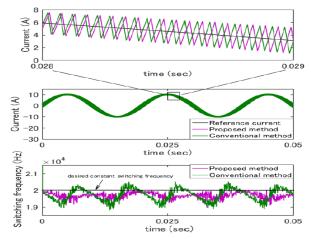

In Figure 10 Current Vs time curve shows the hysteresis current limit response for intended shifting frequency at 20KHZ. The switching frequency Vs time curve displays the nature of operating shifting frequency among planned and traditional approach. It is noticed that the response of operating frequency crosses the intended steady switching frequency of 20 kHz for typical method and it lies below the intended steady switching frequency for planned method.

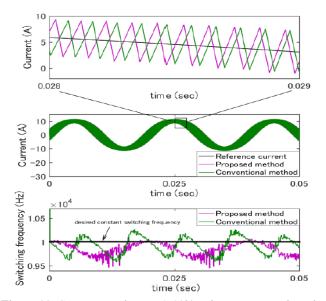

In Figure 11 Current Vs time curve shows the hysteresis current limit response for intended shifting frequency at 10KHZ. It is observed that the output current is similar to reference current. The switching frequency Vs time curve displays the nature of operating shifting frequency among planned and traditional approach. It is noticed that the response of operating frequency crosses the intended steady switching frequency of 10 kHz for typical method and it lies below the intended steady switching frequency for planned method.

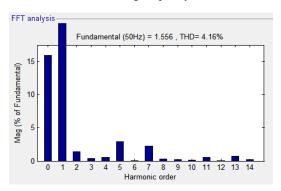

Figure 12 displays FFT analysis of Phase current for digital hysteresis current limit approach. It is observed that digital hysteresis current limit approach for SLQZSI reduces THD in phase current to 4.16% and it is lesser than the typical approaches. Table 2 depicts Performance comparison of Hysteresis current fixed limit, Adjustable hysteresis current limit, and digital hysteresis current limit approach for SLQZSI. Table 2 illustrates the superior performance of digital hysteresis current limit approach compared with hysteresis current fixed limit approach and adjustable hysteresis current limit approach in terms of THD reduction and nature of operating shifting frequency.

**Figure 7:** Schematic diagram of SLQZSI with Digital hysteresis control

Figure 8: Gate pulses for the IGBT switches

**Figure 9:** Current waveform and shifting frequency waveform for the intended shifting frequency at 40KHZ

**Figure 10:** Current waveform and shifting frequency waveform for the intended shifting frequency at 20KHZ

Research Article | Volume 10, Issue 3 | Pages 572-578 | e-ISSN: 2347-470X

Figure 11: Current waveform and shifting frequency waveform for the intended shifting frequency at 10KHZ

Figure 12: FFT analysis of Phase current for digital hysteresis current limit approach

## Table 2: W Performance comparison of three approaches for SLQZSI

| A1                                               | THD    | Intended Shifting Frequency                              |                                                          |                                                       |  |

|--------------------------------------------------|--------|----------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------|--|

| Algorithm                                        |        | 40KHZ                                                    | 20KHZ                                                    | 10KHZ                                                 |  |

| Hysteresis<br>current<br>fixed limit<br>approach | 29.00% | Operating<br>Switching<br>Frequency<br>crosses at<br>4HZ | Operating<br>Switching<br>Frequency<br>crosses at<br>2HZ | Operating<br>Switching<br>Frequency crosses<br>at 1HZ |  |

| Adjustable hysteresis current limit approach     | 7.75%  | Operating<br>Switching<br>Frequency<br>crosses at<br>4HZ | Operating<br>Switching<br>Frequency<br>crosses at<br>2HZ | Operating<br>Switching<br>Frequency crosses<br>at 1HZ |  |

| Digital hysteresis current limit approach        | 4.16%  | Operating<br>Switching<br>Frequency<br>lies below<br>4HZ | Operating<br>Switching<br>Frequency<br>lies below<br>2HZ | Operating<br>Switching<br>Frequency lies<br>below 1HZ |  |

### 7. CONCLUSION

A digital hysteresis current limit controlled SLQZSI has been modeled and simulated successfully using MATLAB Simulink. The simulation result of planned algorithm indicates the THD

in phase current is reduced to 4.16% and optimization solution is chosen such that the following setbacks are satisfied. (i) Shifting frequency is steady and for all time kept at identical or lesser than preferred stable switching frequency (ii) The produced current is steady about the suggestion current (iii) Power loss is minimal. The hypothetical mathematical and simulation outcomes illustrate good performance of planned algorithm over the traditional methods. The planned algorithm may be implemented in future with high-speed Field Programmable Gate array circuit.

### 8. ACKNOWLEDGMENT

The research work is not funded by any public agency.

#### REFERENCES

- [1] Hassan Khalkhali, Arman Oshnoei, Amjad Anvari-Moghaddam, "Proportional Hysteresis Band Control for DC Voltage Stability of Three-Phase Single-Stage PV Systems" Electronics 2022, vol. 11, no. 452. https://doi.org/10.3390/electronics11030452

- [2] Haifeng Wang, Xinzhen Wu, Xiaoqin Zheng, Xibo Yuan, "An improved hysteresis current control scheme during grid voltage zero-crossing for grid-connected three-level inverters", IET Power Electronics, 2021 DOI: 10.1049/pel2.12161

- [3] R.Palanisamy, V.Shanmugasundaram, S.Vidyasagar, K.Vijayakumar, "A Comparative Analysis of Hysteresis Current Control SVM and 3D-SVM for 3-Level NPC Inverter", Journal of Circuits, Systems and Computers 2021, vol. 31, no. 2.

- [4] Petros Karamanakos, Ayman Ayad, Ralph Kennel, "A Variable Switching Point Predictive Current Control Strategy for Quasi-Z-Source Inverters", IEEE Transactions on Industry Applications Year, 2018, vol. 54, no.2.

- [5] H. Komurcugil, S. Bayhan and H. Abu Rub, "Lyapunov function based control approach with cascaded PR controllers for single phase grid tied LCL filtered quasi Z-source inverters," 2017 11th IEEE-International Conference on Compatibility, Power Electronics Power Engineering (CPE-POWERENG), Cadiz, 2017, pp. 510-515. 'doi:10.1109/CPE. 2017.7915224'.

- [6] H. Gong, Y. Li, Y. Wang and R. Zhang, "Input output feedback linearization based control for quasi Z-source inverter in photovoltaic application," 2016 IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, 2016, pp. 1-6. doi: 10.1109/ECCE. 2016. 7855205.

- [7] H. Fathi and H.Madadi, "Enhanced boost Z-source inverters with switched Z-impedance," IEEE Trans. On. I.E., vol. 63, no.2, pp. 691–703, Eab. 2016.

- [8] E. Babaei, E. Shokati Asl, M. Hasan Babayi, and S. Laali, "Developed embedded switched Z-source inverter," IET PE., 2016, vol. 9, no. 9, pp. 1828–1841.

- [9] Nguyen Van, T, Abe. R, "New hysteresis current band digital control for half bridge inverters". In Proceedings of the 2016 IEEE International Conference on Consumer Electronics Taiwan (ICCE-TW), Nantou, Taiwan, pp. 27–29 May 2016

- [10] Nguyen Van, T, Abe. R, "An Indirect Hysteresis Voltage Digital Control for Half Bridge Inverters" in Proceedings of the 2016 IEEE Global Conference on Consumer Electronics, Kyoto, Japan, pp. 11–14, October 2016.

- [11] A. Uphues. K, Ntzold. R, Wegener. S. Soter, "Frequency adaptive PR controller for compensation of current harmonics", Proc. IEEE Indust. Elec. Society (IE-CON), pp. 103-108, 2014.

- [12] Ravindranath. A, Mishra. S. K, and A. Joshi, "Analysis and PWM control of switched boost inverter," IEEETrans. On IE., 2013, vol. 60, no. 12, pp. 5593–5602.

- [13] T. B. Lazzarin, G. A. T. Bauer, and I. Barbi, "A control strategy for parallel operation of single phase voltage source inverters: Analysis,

Research Article | Volume 10, Issue 3 | Pages 572-578 | e-ISSN: 2347-470X

- design and experimental results', IEEE Trans. I.E., 2013, vol. 60, no. 6, pp. 2194-2204.

- [14] M. K. Nguyen, Y. C. Lim, and J. H. Choi, "Two switched inductor quasi Z-source inverters," IET. PE., 2012, vol. 5, no. 7, pp. 1017–1025.

- [15] M. Zhu, K. Yu, and F. L. Luo, "Switched inductor Z-source inverter," IEEE Trans. PE., 2010, vol. 25, no. 8, pp. 2150–2158.

- [16] Y. Tang, S. J. Xie, C. H. Zhang, and Z. G. Xu, "Improved Z-source inverter with reduced Z-source capacitor voltage stress and soft start capability", IEEE Trans. PE., 2009, vol. 24, no. 2, pp. 409–415.

- [17] M. Liserre, R. Teodorescu, F. Blaabjerg, "Stability of photo voltaic and wind turbine grid connected inverters for a large set of grid impedance values", IEEE Trans-P.E., 2006, vol. 21, no. 1, pp. 263-272.

- [18] Zare, F. Ledwich, G. "A hysteresis current control for single-phase multilevel voltage source inverters PLD implementation", IEEE Trans. Power Electron. 2002, 17, pp. 731–738.

© 2022 by V. Malathi, Dr. S. Sentamil Selvan and Dr. S. Meikandasivam. Submitted for possible open access publication under the

terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).